🛑pdf를 보고 제 주관으로 해석하고 적은 글이기에 정확하지 않을 수 있습니다

📕The words of a computers's language are called instructions

📕Instruction Instruction Set Architecture

📗instruction의 정의

- 프로세서의 operation을 묘사하는 기본적인 명령어이다.

- 인스트럭션은 하드웨어와 소프트웨어 사이에 있다.

📗instruction의 구성요소

- Opcode(i.e., operation code) : instruction이 해야 할 행동

- Operands: the object of an operation

📕ISA

- 약칭 Instruction set architecture

- 프로세서가 이해하는 instruction의 집합이다.

- 다른 프로세스는 다른 ISA를 가진다.

- 하지만 프로세스들은 서로 다른 프로세스에 걸쳐있습니다.

- 이유

- 유사한 원리에 기반한 유사한 하드웨어 기

- 모든 시스템이 제공해야 하는 몇 가지 공통적이고 기본적인 Operations

- 이유

📕Microarchietecture

- Microarchietecture는 특정한 설계 제약 조건과 목표에 따른 ISA를 구현한것입니다.

- 사양을 만족하는 한 이식은 다양하게 가능하다.

- 소프트웨어에 노출되지 않고 하드웨어에서 수행되는 모든 작업할 수 있습니다.

- Pipelining

- Speculative execution

- Memory access scheduling

- Arithmetic units

📕CISC VS RISC

📗CISC

- Complex Instruction Set Computer

- 오래된 설계

- 복잡하고 다양한 길이의 instructions

- ISA에서 지원되는 강력한 instructions

📗Pros

- 어셈블리 프로그래밍을 더욱 쉽게 한다. --> 컴파일러가 간단하다.

- instruction 메모리 사용을 줄여준다.

📗Cons

- CPU 설계가 어렵다

📗RISC

- Reduced Instruction Set Computer

- CISC보다는 최신적 개념

- 간단하고 표준화된 instructions

- Small instruction set : CISC type operation becomes a chain of RISC operations

- e.g.) ARAM , MIPS , SPARC, RISC-V

📗Pros

- CPU 설계가 쉽다.

- 작은 instruction 집합 -> clok의 속도가 빨라진다.

📗Cons

- 어셈블리 언어는 전형적으로 길다.

- 메모리의 사용이 무겁다.

💡현대의 x86 프로세서들의 대부분은 RISC 기술을 사용해서 구현되었다.

📕RISC - V

- RISC - V는 RISC 원칙에 기반을 둔 개방형 표준 ISA이다.

- UC Berkeley에 의해 설계되었다.

- 전형적인 현대 ISAs

- 비슷한 ISAs는 임베디드 코어 시장에서 많은 점유율을 가지고 있다.

📕Operands of the Computer Hardware

📗The RISC-V assembly language notation

add a, b, c -> a=b+c

컴퓨터에게 두 개의 변수 b와 c를 더해서 그 합을 a에 넣으라고 지시하는 명령어

📗모든 RISC-V의 산술 operations은 같은 형태를 가진다.

- 세 개의 변수 : 두 개의 sources와 하나의 destination

💻4개의 변수의 합을 a에 넣는 과정

add a , b, c // b와 c의 합을 a에 넣어라.

add a, a, d // a(b+c)와 d의 합을 a에 넣어라.

add a, a, e // a(b+c+d)와 e의 합을 a에 넣어라.

📗설계 원칙 1

단순함은 규칙성을 선호한다!

- 규칙성은 구현을 간단하게 만들어준다.

- 단순함은 적은 비용으로 높은 성능을 가능하게 한다.

📗산술, 연산 instructions은 register operands 사용한다.

- 레지스터는 하드웨어의 설계를 이용한 초기의 저장공간이다.

📗RISC - V는 32-bit register file를 32개 가지고 있다. : x0~x31

- 데이터에 접근하는 데 사용한다.

- 32-bit data는 word라고 부른다.

- 64-bit data는 doubleworld라고 부른다.

📗설계 원칙 2

작을수록 더 빠르다!

- 많은 수의 레지스터는 clock cycle을 증가시킬지도 모른다.

- 레지스터수와 성능 간의 교환 -> 작을수록 빠르다!

📕Memory Operands

- 배열 및 구조와 같은 복합 데이터에 사용되는 기본 메모리

- 레지스터는 제한되어 있기에 복합 데이터를 처리하는데 적합하지 않다.

- RISC의 산술 연산은 레지스터를 통해서만 발생하기 때문에 데이터 안에 있는 복잡한 데이터를 처리하기 위해 아래와 같은 명령어를 적용한다.

- Load values from memory to register ( memory->register)

- Store result from register to memory (register -> memory)

- 데이터 전송 명령은 레지스터와 메모리 간에 데이터를 전송하는 데 사용됩니다.

📕Memory Addressing

- 메모리 안에 있는 word에 접근하기 위해서 인스트럭션은 메모리 주소를 제공해야 한다.

- 메모리는 주소가 0부터 시작하는 해당 배열의 인덱스 역할을 하는 대규모 단일 차원 배열일 뿐입니다.

- 8-bit bytes는 많은 프로그램에서 유용하다. -> 사실상 모든 아키텍처가 개별 바이트를 처리함

- word의 바이트 주소가 word 내의 4바이트 중 하나의 주소와 일치합니다

- word는 32 bit인데 1byte는 8bit이기에 word는 4바이트이다?

- 순차적인 워드의 주소는 4로 나뉜다. (0, 4, 8, 12 ,,,)

📕Endian

📗RISC - V는 little endian processor!

- 가장 작은 바이트가 가장 작은 워드의 주소에 매핑되는 방식.

📗Little Endian vs Big Endian

- Big - Endian : 데이터의 가장 큰 바이트가 가장 작은 주소에 매핑됨.

- Little - Endian : 데이터의 가장 작은 바이트가 가장 작은 주소에 매핑됨.

아래 그림을 보면 훨씬 이해가 쉬울 것이다.

0x00112233은 33이 가장 하위 byte이고, 00이 가장 상위 byte이다.

Big-endian에서는 가장 작은 주소에 상위 byte가 들어가고 그다음으로 큰 byte가 위치하는 구조입니다.

little-endian에서는 가장 작은 주소에 하위 byte가 들어가고 그다음으로 작은 byte가 위치하는 구조입니다.

📗RISC-V는 메모리에 words를 정렬할 필요가 없습니다.

- words는 4의 배수인 주소로 시작할 필요가 없기 때문입니다

💡RISC-V는 misalign 방식을 허용하기 때문에 4의 배수로 시작할 필요가 없다고 합니다.

📕Memory Operand Example

📗Compiling Using Load and Store

💻C code

A [12] = h + A [8];

- h는 x21 레지스터에 있다고 가정을 한다.

- A는 4-byte int형 배열이고, 주소는 x 22번을 기반으로 한다.

💻Compiled RISC-V code :

lw x9, 32(x22) //x9 레지스터 안에 A [8]을 불러온다.

add x9, x21, x9 // x9 레지스터 안에 x21안에 있는 h와 x9 안에 있는 A[8]을 더한 값을 넣는다.

sw x9, 48(x22) // x9 레지스터 안에 있는 값을 int 형 배열인 A에 48/4 index에 저장한다.

lw : load word

sw : stroe word

x22앞에 있는 숫자들은 index를 뜻하는데 4byte 배열이기에 나누기 4할 값이 해당 index가 된다.

28(x22) --> 28/4 =7 ->> A [7]

📕Register Vs memory

📗레지스터는 메모리보다 액세스 속도가 월등히 빠릅니다.

왜?

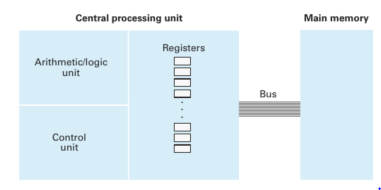

- 그림을 자세히 보면 메인 메모리는 직접적으로 ALU에 접근하지 못합니다.

- (Bus나 레지스터를 통해서 접근해야 함)

- 따라서 레지스터가 메모리보다 접근 속도가 훨씬 빠릅니다.

📗메모리에 있는 데이터를 사용하기 위해선 load와 stores 외에도 많은 명령어가 필요합니다.

📗컴파일러는 가능한 한 변수에 레지스터를 사용해야 합니다.

- 덜 자주 사용되는 변수의 경우 메모리로만 유출 (레지스터에 할당 x)

- 레지스터 최적화는 중요하다.

- 방에서 물건을 자주 사용하는 건 근처에 두는 것처럼 자주 사용하는 레지스터는 최적화를 하는 것이 성능적으로 중요합니다.

📕Constant or Immediate Operands

📗프로그램은 연산에서 상수를 사용하는 경우가 많습니다.

📗RISC - V의 인스트럭션에 상수 데이터를 지정할 수 있습니다.

💡addi : addition with immediate value

addi x22, x22, 4(immediate value [constant]) // x22= x22+4

📗Constant operands는 자주 발생합니다.

- addi는 RISC-V 프로그램에서 가장 자주 사용되는 명령어이다.

📗immediate 연산자를 사용하는 인스트럭션

- 메모리에서 불러오는 상수를 쓰는 것보다 훨씬 빠르고 에너지 소비가 적다.

📗RISC-V는 상수 0을 레지스터 x0에 고정시킴으로써 제공한다.

- 상수 0은 일반적인 작업에서 유용하게 사용된다.

- sub x1, x0, x1 -> x1= 0-x1

- x0 = 항상 0으로 고정된다.

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [computer archiecture] - arithmetic_for_computers(1) (0) | 2022.10.19 |

|---|---|

| [computer architecture]-instruction_language_of_computer(3) (0) | 2022.10.11 |

| [computer architecture]-instructions_language_of_computer(2) (0) | 2022.10.09 |

| [computer architecture] -Computer Abstractions and Technology (2) (0) | 2022.09.29 |

| [Computer architecture] - Computer Abstractions and Technology (1) (2) | 2022.09.22 |